Alivio April Checkin

Last edited: August 8, 2025- Want to interview more severe ashma

- Want to find someone younger

Difference between marketing and purchaser.

Taking to people

Spoke with Matt. Talked with more details with prototyping and how they can build a unique product.

Have not gotten back to him yet.

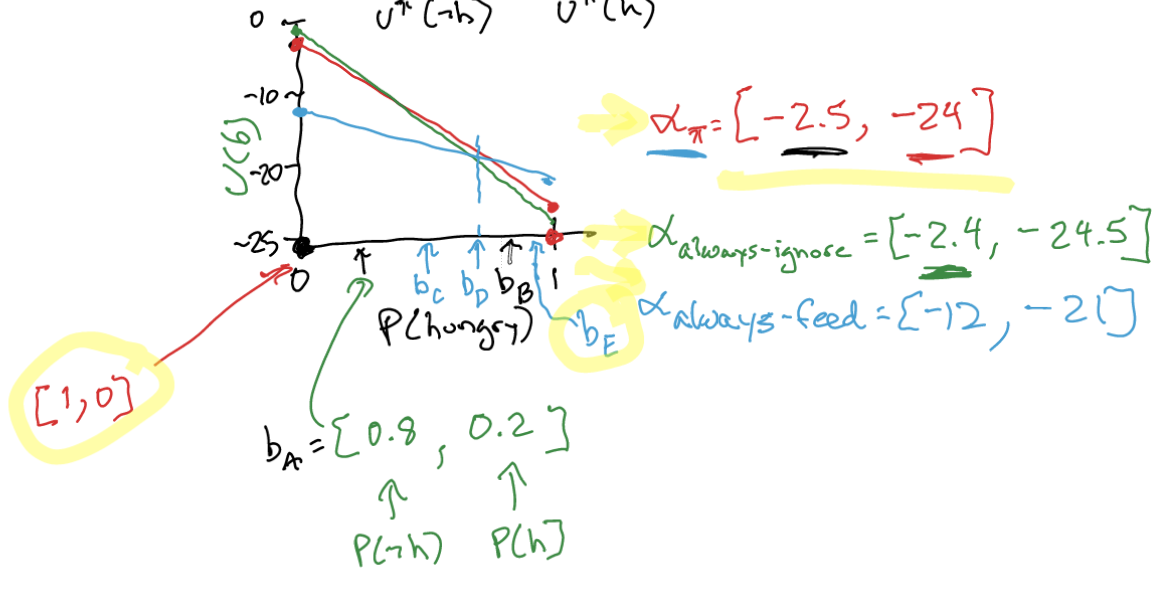

alpha vector

Last edited: August 8, 2025Recall, from conditional plan evaluation, we had that:

\begin{equation} U^{\pi}(b) = \sum_{s}^{} b(s) U^{\pi}(s) \end{equation}

let’s write it as:

\begin{equation} U^{\pi}(b) = \sum_{s}^{} b(s) U^{\pi}(s) = {\alpha_{\pi}}^{\top} b \end{equation}

where \(\U_{\pi}(s)\) is the conditional plan evaluation starting at each of the initial states.

\begin{equation} \alpha_{\pi} = \qty[ U^{\pi}(s_1), U^{\pi}(s_2) ] \end{equation}

You will notice, then the utility of \(b\) is linear on \(b\) for different policies \(\alpha_{\pi}\):

At every belief \(b\), there is a policy which has the highest \(U(b)\) at that \(b\) given be the alpha vector formulation.

alphabet

Last edited: August 8, 2025see also in programming string (C)

- an alphabet \(\Sigma\) is a finite set

- a finite-sequence of elements in \(\Sigma\) is called a string

- the set of all strings in \(\Sigma\) is called \(\Sigma^{*}\), which includes the empty string

- for a particular string \(x\), the length of it is \(|x|\)

- the string of length zero is called \(\varepsilon\)

- a language is a subset of \(\Sigma^{*}\), meaning its a set of strings

Omer seems to call strings “words” sometimes.

languages are boolean function over strings

For every language \(L\) over \(\Sigma\) corresponds to a unique function \(f: \Sigma^{*} \to \{0,1\}\), whereby if \(f(x) = 1\), then \(x \in L\); otherwise, if \(f(x) = 0\), \(x \not \in L\).

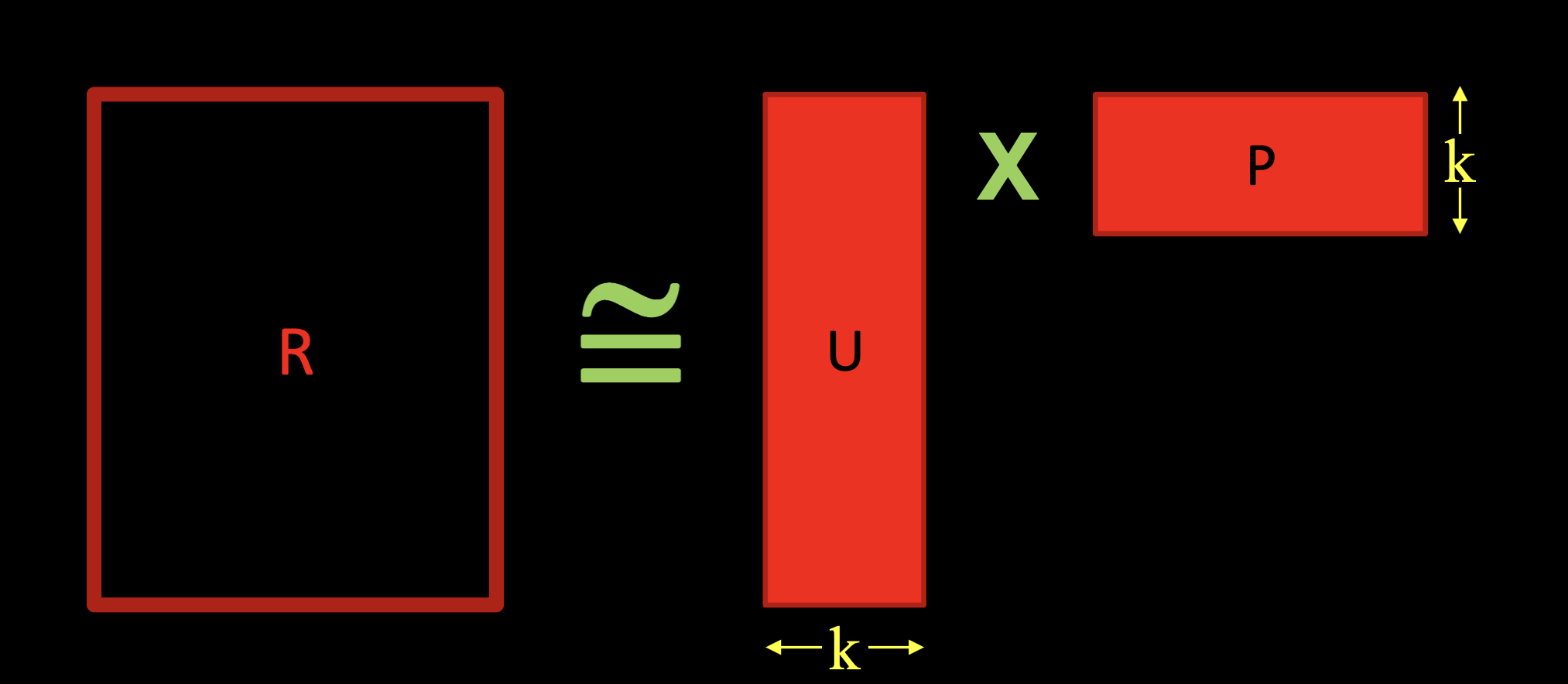

Alternating Least Squares

Last edited: August 8, 2025Alternating Least Squares is a method to Factoring a matrix into two components:

\begin{equation} \mathcal{M}( R) \approx \mathcal{M}(U) \cdot \mathcal{M}(P) \end{equation}

where, we want to come up matricies \(U\) and \(P\) with a certain side length \(k\) that we exdogenously come up with

To perform Alternating Least Squares, we fix the values of either \(U\) or \(P\), then perform the least-squares optimization on

(This is proven best-fit for “non-pathological matricies”)

Ambulance Trajectories

Last edited: August 8, 2025Problem: current ambulance routing don’t optimize significantly on the contextual cases for stroke patients

Stroke hospitals: PSC is smaller than a CSC.

Previous work

Routing methods—

- route all patient to nearest PSC, which is worse than

- route high risk patient to CSC, which is worse than

- always route to CSC

This is counter-intuitive. How do we solve, given a stroke condition, available PSC/CSC locations, traffic, etc., for where and how to route a patient?